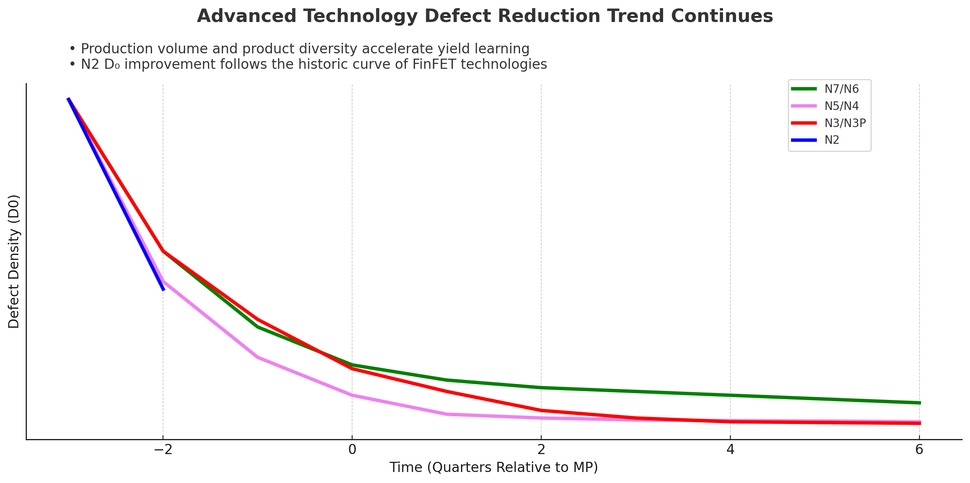

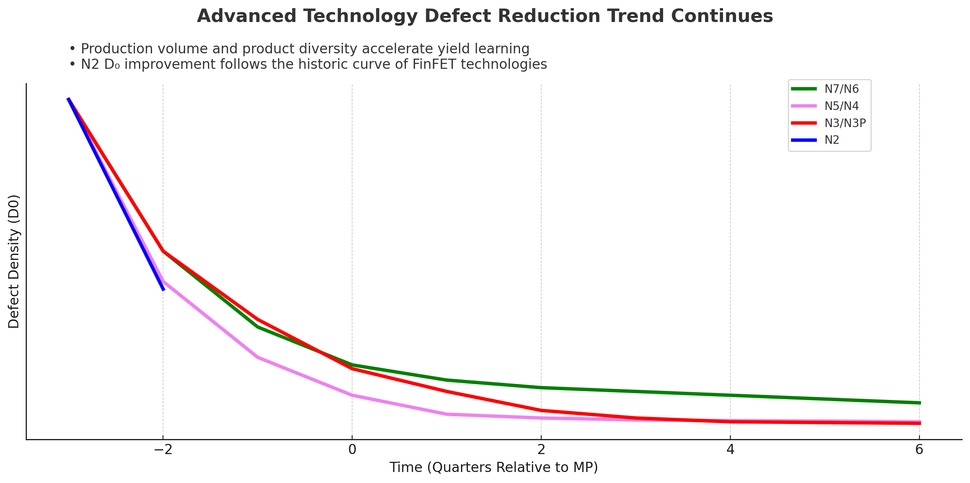

TSMC baru -baru ini diumumkan pada seminar teknologi Amerika Utara Ketumpatan Kecutan (D0) teknologi proses N2 (2nm) berbanding dengan proses pendahulunya pada peringkat yang sama.Menurut syarikat itu, ketumpatan kecacatan N2 lebih rendah daripada N3 (3nm), N5 (5nm), dan N7 (7nm) nod pembuatan.Di samping itu, slaid menunjukkan bahawa proses N2 TSMC masih dua suku dari pengeluaran besar -besaran, yang bermaksud TSMC dijangka mula menghasilkan cip 2nm menjelang akhir suku keempat tahun 2025 seperti yang diharapkan.

Walaupun proses N2 TSMC adalah teknologi proses pertama syarikat untuk mengadopsi transistor nanosheet Cincin Penuh (GAA), ketumpatan kecacatan nod ini lebih rendah daripada proses generasi terdahulu pada peringkat yang sama, dua suku menjelang pengeluaran massa (MP).Proses generasi sebelumnya- N3/N3p, N5/N4, dan N7/N6- Semua transistor kesan medan sirip matang (FinFET).Oleh itu, walaupun N2 adalah nod pertama TSMC untuk mengadopsi transistor nanosheet GAA, pengurangan ketumpatan kecacatannya lebih besar daripada proses generasi terdahulu sebelum memasuki tonggak pengeluaran besar -besaran (HVM).

Carta ini menggambarkan variasi ketumpatan kecacatan dari masa ke masa, merangkumi dari tiga suku sebelum pengeluaran besar -besaran hingga enam suku selepas pengeluaran besar -besaran.Di antara semua nod yang dipaparkan - N7/N6 (hijau), N5/N4 (ungu), N3/N3p (merah), dan N2 (biru) - ketumpatan kecacatan berkurangan dengan peningkatan hasil, tetapi kadar penurunan berbeza -beza bergantung kepada kerumitan nod.Perlu diingat bahawa N5/N4 adalah yang paling aktif dalam mengurangkan kecacatan awal, sementara peningkatan hasil N7/N6 agak lembut.Tahap kecacatan awal lengkung N2 lebih tinggi daripada N5/N4, tetapi kemudian menurun dengan ketara, yang sangat dekat dengan trajektori pengurangan kecacatan N3/N3p.

Slaid menekankan bahawa hasil dan kepelbagaian produk kekal sebagai faktor pemacu utama untuk mempercepatkan peningkatan ketumpatan kecacatan.Pengeluaran dan produk yang lebih besar menggunakan proses yang sama dapat mengenal pasti dan membetulkan ketumpatan kecacatan dan hasil hasil lebih cepat, membolehkan TSMC mengoptimumkan kitaran pembelajaran kecacatan.TSMC menyatakan bahawa teknologi pembuatan N2nya telah memperoleh lebih banyak cip baru daripada teknologi pendahulunya (kerana TSMC kini menghasilkan cip N2 untuk pelanggan telefon pintar dan pengkomputeran berprestasi tinggi (HPC) berisiko), dan keluk penurunan ketumpatan kecacatan pada dasarnya mengesahkan ini.

Memandangkan faktor risiko yang dibawa oleh pengenalan seni bina transistor baru, sangat penting untuk kadar pengurangan kecacatan N2 untuk kekal konsisten dengan nod berasaskan FinFET sebelumnya.Ini menunjukkan bahawa TSMC telah berjaya memindahkan kepakaran pembelajaran dan kecacatan prosesnya ke era gaafet baru tanpa menghadapi kemunduran yang ketara.

RFQs/Pesanan (0)

RFQs/Pesanan (0)

RFQs/Pesanan (0)

RFQs/Pesanan (0)